/

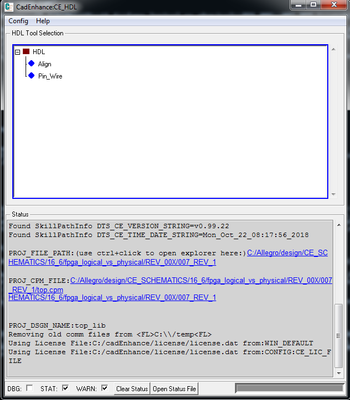

CE-HDL

CE-HDL

Page Map:

On This Page:

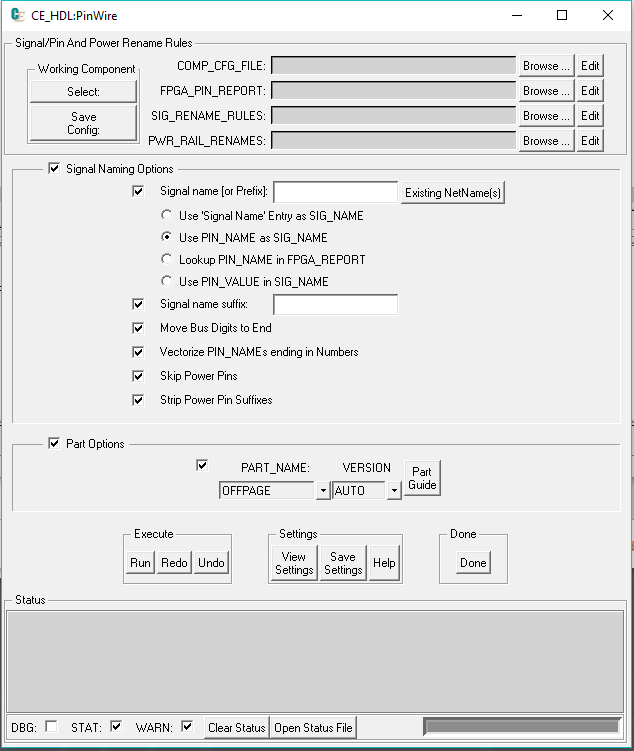

CE-HDL:PinWire

- The PinWire plugin provides the capability to instantly add large numbers of named wire connections to symbols in the schematic.

- PinWire uses the symbol pinNames as a starting point to create the SIG_NAME property that gets attached to each wire.

- The wires start at the component pin and can be terminated to OFFPAGES, IOPORTS, or selected versions of components like capacitors and resistors.

- The OFFPAGE and IOPORT types are selected based on the pinType which is determined by reading the component library information.

- The user may specify a prefix or suffix to be added to the SIG_NAME.

- The user can also provide a list of renaming rules to apply to create flexible SIG_NAMES per wire.

- A set of rename rules can be created and stored for each component

- PinWire can also use an FPGA Pin Report to find the proper SIG_NAME to attach to a wire connected to an FPGA Pin.

- This feature alone can save hours to days worth of schematic capture work while also providing unparalleled accuracy.

- The user can also use an interactive GUI to create and define the what nets and voltages symbol power pins will be connected to.

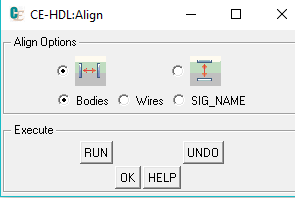

CE-HDL:Align

- The Align plugin enables the user to align components, and netnames in their schematics providing a very efficient means to produce a polished, professional looking schematic in seconds.

, multiple selections available,

Related content

Helpful Videos for CE-HDL

Helpful Videos for CE-HDL

More like this

Symbol Description Language (SDL)

Symbol Description Language (SDL)

More like this

EDA Symbol Conversion

EDA Symbol Conversion

More like this

Smart SIG_NAME(s) Entry

Smart SIG_NAME(s) Entry

More like this

PartBuilder

PartBuilder

More like this

The PinWire Gui

The PinWire Gui

More like this